Introduction:

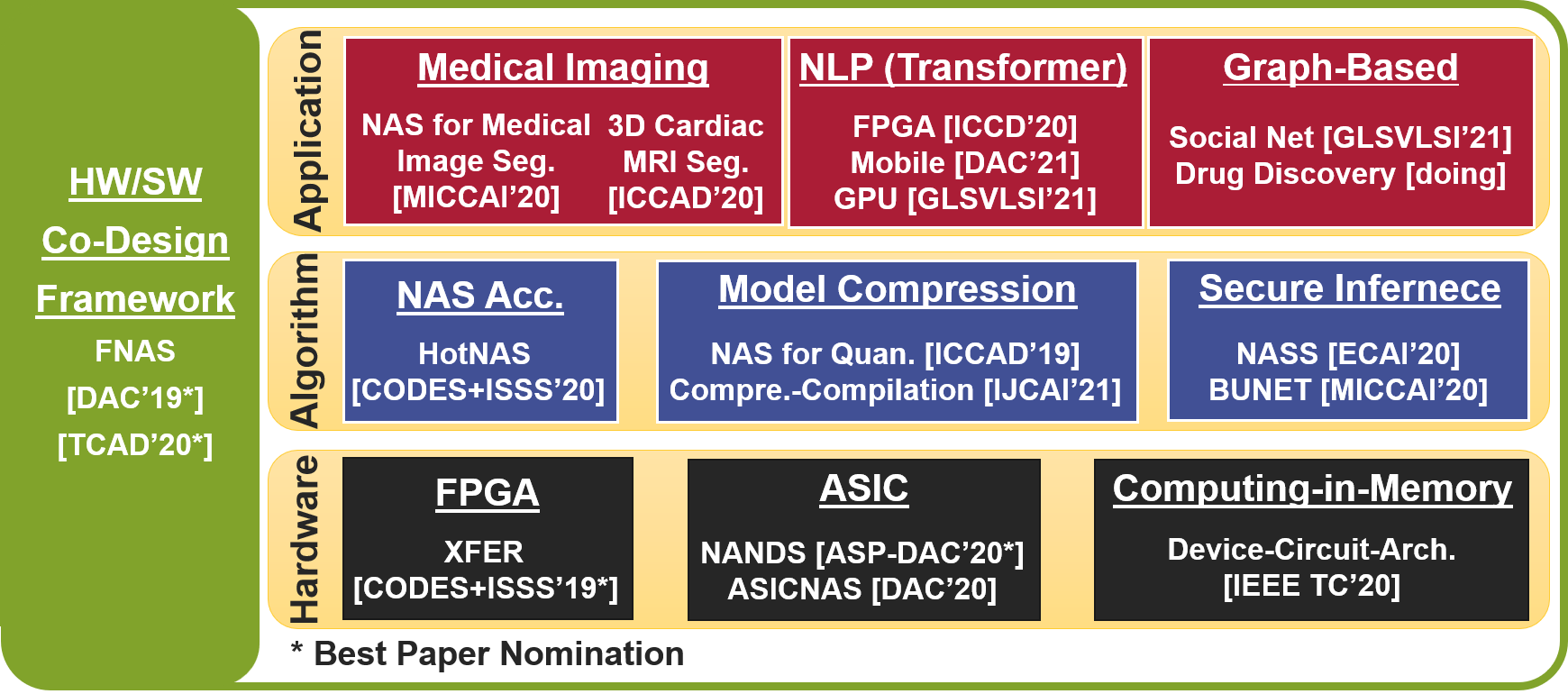

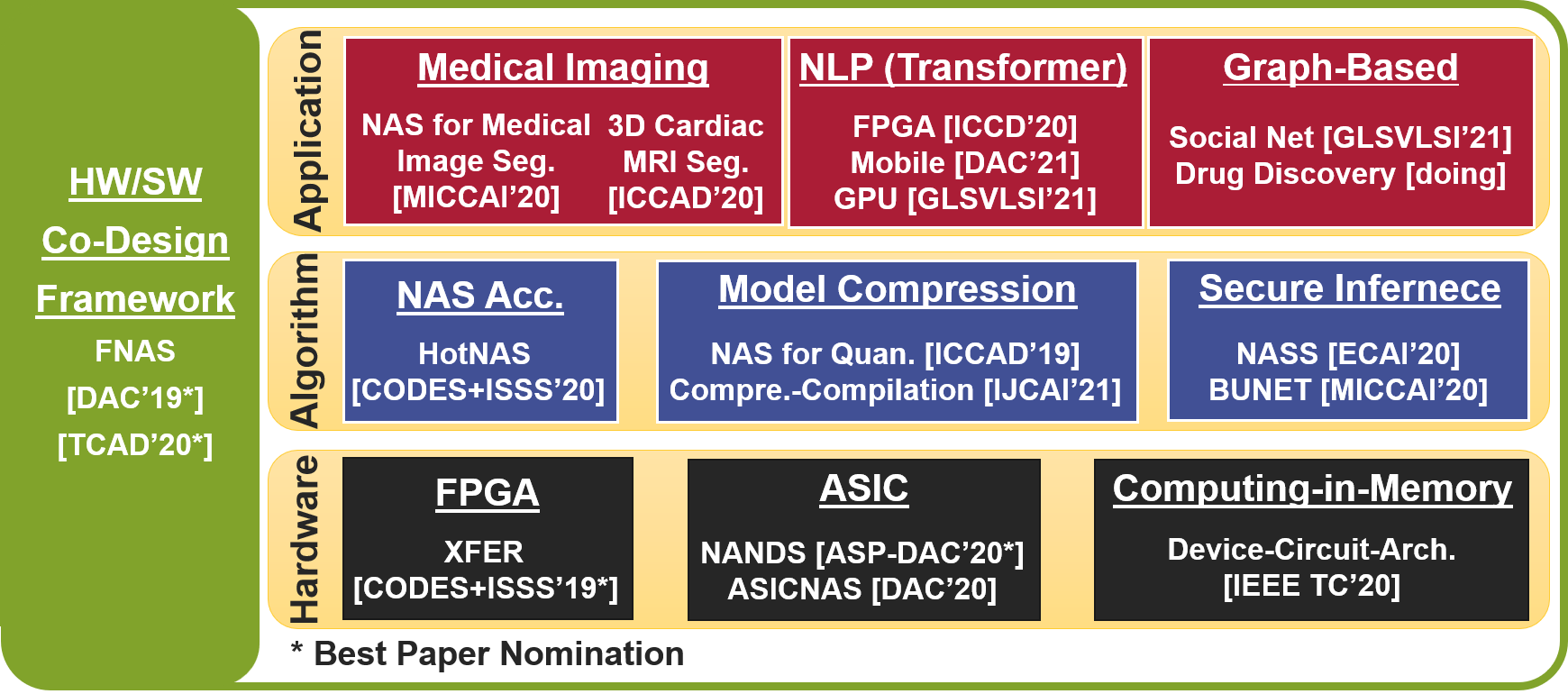

Throughout our studies in these years (2019-Now), we have built the full stack for the co-design of the AI system using AutoML. The above figure demonstrates this stack in three layers: Application, Algorithm, and Hardware (see feature works [here](../../2017/06/01/research_nnFPGA/HW_NAS.pdf)).

Members:

Weiwen Jiang

Xinyi Zhang (Ph.D. candidate @ PITT)

Qing Lu (Ph.D. candidate @ ND)

Lei Yang (Postdoc @ GWU)

Publications:

1.

SimDisQ-Layout: Simulating Circuit Layout for Distributed Quantum Computing [arXiv]

Sen Zhang, Yipie Liu, Brian Mark, Weiwen Jiang, Zebo Yang, and Lei Yang

Accepted by Optical Fiber Communication (OFC), 2026

2.

A collaboration strategy in the mining pool for proof-of-neural-architecture consensus

Boyang Li, Qing Lu, Weiwen Jiang, Taeho Jung, Yiyu Shi

Blockchain: Research and Applications, 100089, 2022

3.

A Length Adaptive Algorithm-Hardware Co-design of Transformer on FPGA Through Sparse Attention and Dynamic Pipelining

Hongwu Peng, Shaoyi Huang, Shiyang Chen, Bingbing Li, Tong Geng, Ang Li, Weiwen Jiang, Wujie Wen, Jinbo Bi, Hang Liu and Caiwen Ding

Accepted by Design Automation Conference (DAC), 2022

4.

Hardware and neural architecture co-search

Sakyasingha Dasgupta, Weiwen Jiang, Yiyu Shi

PUS Patent App. 17/362,997, 2022/7

5.

Hardware/Software Co-Exploration for Graph Neural Architectures on FPGAs []

Qing Lu, Weiwen Jiang, Meng Jiang, Jingtong Hu, Yiyu Shi

Proc. IEEE Computer Society Annual Symposium on VLSI(ISVLSI), 2022/7

6.

The Larger The Fairer? Small Neural Networks Can Achieve Fairness for Edge Devices [arXiv]

Yi Sheng, Junhuan Yang, Yawen Wu, Kevin Mao, Yiyu Shi, Jingtong Hu, Weiwen Jiang and Lei Yang

Accepted by Design Automation Conference (DAC), 2022

7.

RADARS: Memory Efficient Reinforcement Learning Aided Differentiable Neural Architecture Search

Zheyu Yan, Weiwen Jiang, Xiaobo Sharon Hu, Yiyu Shi

2022 27th Asia and South Pacific Design Automation Conference (ASP-DAC), 128-133,

8.

One Proxy Device Is Enough for Hardware-Aware Neural Architecture Search

Bingqian Lu, Jianyi Yang, Weiwen Jiang, Yiyu Shi and Shaolei Ren,

ACM SIGMETRICS/Performance, 2022

9.

Dancing along Battery: Enabling Transformer with Run-time Reconfigurability on Mobile Devices [arXiv]

Y. Song, W. Jiang, B. Li, P. Qi, Q. Zhuge, E. H.-M. Sha, S. Dasgupta, Y. Shi, and C. Ding

Accepted by Design Automation Conference (DAC), 2021

10.

Optimizing FPGA-based Accelerator Design for Large-Scale Molecular Similarity Search

Hongwu Peng, Shiyang Chen, Zhepeng Wang, Junhuan Yang, Scott A. Weitze, Tong Geng, Ang Li, Jinbo Bi, Minghu Song, Weiwen Jiang, Hang Liu, Caiwen Ding,

Accepted by IEEE/ACM International Conference On Computer-Aided Design (ICCAD), Virtual, 2021. (Invited paper)

11.

FL-DISCO: Federated Generative Adversarial Network for Graph-based Molecule Drug Discovery

D. Manu, Y. Sheng, Junhuan Yang, Jieren Deng, Tong Geng, Ang Li, Caiwen Ding, Weiwen Jiang, Lei Yang,

Accepted by IEEE/ACM International Conference On Computer-Aided Design (ICCAD), Virtual, 2021. (Invited paper)

12.

Federated Contrastive Learning for Dermatological Disease Diagnosis via On-device Learning

Y. Wu, D. Zeng, Z. Wang, Y. Sheng, L. Yang, A. James, Y. Shi, J. Hu,

Accepted by IEEE/ACM International Conference On Computer-Aided Design (ICCAD), Virtual, 2021. (Invited paper)

13.

RMSMP: A Novel Deep Neural Network Quantization Framework with Row-wise Mixed Schemes and Multiple Precisions

S. Chang, Y. Li, M. Sun, W. Jiang, S. Liu, Y. Wang and X. Lin,

Proc. 2021 IEEE/CVF International Conference on Computer Vision (ICCV),

14.

DIAN: Differentiable Accelerator-Network Co-Search Towards Maximal DNN Efficiency

Y. Zhang, Y. Fu, W. Jiang, C. Li, H. You, M. Li, V. Chandra and Y. Lin

in Proc. of ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED),

15.

A Compression-Compilation Framework for On-mobile Real-time BERT Applications

W. Niu, Z. Kong, G. Yuan, W. Jiang, J. Guan, C. Ding, P. Zhao, S. Liu, B. Ren, Y. Wang

Demo Paper at International Joint Conference on Artificial Intelligence (IJCAI-21),

16.

Work in Progress: Mobile or FPGA? A Comprehensive Evaluation on Energy Efficiency and a Unified Optimization Framework

G. Yuan, P. Dong, M. Sun, W. Niu, Z. Li, Y. Cai, J. Liu, W. Jiang, X. Lin, B. Ren, X. Tang, Y. Wang

IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS), Virtual, May. 2021.

17.

Accelerating Transformer-based Deep Learning Models on FPGAs using Column Balanced Block Pruning

H Peng, S Huang, T Geng, A Li, W. Jiang, H Liu, S Wang, C Ding

in Proc. of International Symposium on Quality Electronic Design (ISQED),

18.

Achieving Full Parallelism in LSTM via a Unified Accelerator Design

X. Zhang, W. Jiang, J. Hu

IEEE International Conference on Computer Design (ICCD2020@Online), Oct. 2020.

(acceptance rate 62/221=28.1%)

19.

Hardware Design and the Competency Awareness of a Neural Network

Y. Ding, W. Jiang, Q. Lou, J. Liu, J. Xiong, X. Sharon Hu, X. Xu, and Y. Shi,

Nature Electronics, Aug. 2020 (in print)

20.

Standing on the Shoulders of Giants: Hardware and Neural Architecture Co-Search with Hot Start [arXiv]

W. Jiang, L. Yang, S. Dasgupta, J. Hu and Y. Shi

International Conference on Hardware/Software Co-design and System Synthesis CODE+ISSS) in ESWEEK'20

(acceptance rate 94/375=25.1%)

also appears at IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), Virtaul Conference, Oct. 2020.

21.

Towards Cardiac Intervention Assistance: Hardware-Aware Neural Architecture Exploration for Real-Time 3D Cardiac Cine MRI Segmentation

D. Zeng, W. Jiang, T. Wang, X. Xu, H. Yuan, M. Hung, J. Zhuang, J. Hu and Y. Shi,

Proc. IEEE/ACM International Conference On Computer-Aided Design (ICCAD), Virtual, 2020. (Invited paper)

22.

Device-Circuit-Architecture Co-Exploration for Computing-in-Memory Neural Accelerators [arXiv]

W. Jiang, Q. Lou, Z. Yan, L. Yang, J. Hu, X. S. Hu and Y. Shi

IEEE Transactions on Computers (TC), Accepted, 2020.

23.

BUNET: Blind Medical Image Segmentation Based on Secure UNET

S. Bian, X. Xu, W. Jiang, Y. Shi

in Proc. of Medical Image Computing and Computer Assisted Interventions (MICCAI), Lima, Peru, 2020.

(acceptance rate 30%)

24.

MS-NAS: Multi-Scale Neural Architecture Search for Medical Image Segmentation

X. Yan, W. Jiang, Y. Shi, C. Zhuo

in Proc. of Medical Image Computing and Computer Assisted Interventions (MICCAI), Lima, Peru, 2020.

(acceptance rate 30%)

26.

Co-Exploration of Neural Architectures and Heterogeneous ASIC Accelerator Designs Targeting Multiple Tasks [arXiv]

L. Yang, Z. Yan, M. Li, H. Kwon, L. Lai, T. Krishana, V. Chandra, W. Jiang, and Y. Shi

Design Automation Conference (DAC), 2020.

(acceptance rate 228/992=23.0%)

27.

NASS: Optimizing Secure Inference via Neural Architecture Search [arXiv]

B. Song, W. Jiang, Q. Lu, Y. Shi and T. Sato

Proc. European Conference on Artificial Intelligence (ECAI), Santiago de Compostela, June. 2020.

(acceptance rate 365/1363=26.8%)

28.

Co-Exploring Neural Architecture and Network-on-Chip Design for Real-Time Artificial Intelligence (BEST PAPER NOMINATION)

L. Yang, W. Jiang, W. Liu, E. H.-M. Sha, Y. Shi and J. Hu

Proc. Asia and South Pacific Design Automation Conference (ASP-DAC), Beijing, Jan. 2020.

(acceptance rate 86/263=32.6%)

29.

Achieving Super-Linear Speedup across Multi-FPGA for Real-Time DNN Inference [arXiv][slides] (BEST PAPER NOMINATION)

W. Jiang, E. H.-M. Sha, X. Zhang, L. Yang, Q. Zhuge, Y. Shi and J. Hu

International Conference on Hardware/Software Co-design and System Synthesis CODE+ISSS) in ESWEEK'19

(acceptance rate 66/243=27.2%)

also appears at ACM Transactions on Embedded Computing Systems (TECS), NYC, New York, USA, Oct. 2019.

30.

Integrating Memristors and CMOS for Better AI

W. Jiang, B. Xie, C-C Liu and Y. Shi,

Nature Electronics (News and Views), Sep. 2019

31.

On Neural Architecture Search for Resource-Constrained Hardware Platforms

Q. Lu, W. Jiang, X. Xiao, J. Hu and Y. Shi,

Proc. IEEE/ACM International Conference On Computer-Aided Design (ICCAD), Westminster, CO, 2019. (Invited paper)

32.

When Neural Architecture Search Meets Hardware Implementation: from Hardware Awareness to Co-Design

X. Zhang, W. Jiang, Y. Shi and J. Hu,

Proc. IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Miami, Florida, USA, Aug. 2019. (Invited paper)

33.

Accuracy vs. Efficiency: Achieving Both through FPGA-Implementation Aware Neural Architecture Search [arXiv]

(BEST PAPER NOMINATION)

W. Jiang, X. Zhang, E. H.-M. Sha, L. Yang, Q. Zhuge, Y. Shi, and J. Hu

Design Automation Conference (DAC), 2019.

(acceptance rate 204/815=25%)

34.

Heterogeneous FPGA-based Cost-Optimal Design for Timing-Constrained CNNs

W. Jiang, E. H.-M. Sha, Q. Zhuge, L. Yang, X. Chen, and J. Hu

International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES) in ESWEEK'18

(acceptance rate 67/270=24.8%)

also appear at IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), Torino, Italy, Oct. 2018.

Hornors: